Antenna Effect는 Channel 면적이 작을수록 문제가 생길 여지가 크기 때문에

갈수록 어려워지는 불량종류입니다.

1. Antenna Effect

플라즈마에 의해 gate oxide가 damage를 입는 것으로,

검출은 oxide가 깨짐으로써 STBY current가 줄줄 새는 걸로 알 수 있습니다.

이러한 문제는 수율과 신뢰성에 큰 영향을 끼칩니다.

주로 MOS 공정중에 ETCH 공정에서 일어납니다.

ETCH를 위해 plasma를 쓰게 되는데 면적이 넓을수록, 두께가 두꺼울수록,

많은 양의 plasma가 쌓이고 일정이상 쌓인 plasma는 빠져나갈 데를 찾다가

gate oxide의 Breakdown Voltage를 넘어서는 순간

gate oxide를 통해 한번에 빠져나가면서 damage를 주는 것입니다.

각 ETCH 공정 후에 CMP를 진행하면서 plasma도 같이 제거되기 때문에

각 단계별 Metal, contact 공정 하나만 고려하면됩니다.

2 Antenna Rule

이러한 Antenna Effect를 방지하기 위해 Layout의 Design Rule에 antenna rule이 있습니다.

plasma가 빠져나가는 밀도와 관계가 있기에

gate oxide의 면적이 넓을수록 Metal의 면적이 작을수록 좋습니다.

Metal 면적 / Channel 면적

으로 수식이 간단히 사용되고, 이 값은 gate oxide에 따라서 다른 값을 가지게 됩니다.

또한 diode나 diffusion영역의 연결에 따라 달라지게 됩니다.

diffusion에 연결된다면 그쪽으로 plasma가 빠져나가기 때문에 antenna effect에 유리합니다.

갈수록 TR은 작아지기 때문에 분모가 작아져서 연결 할 수 있는 Metal의 면적도 작아지기 때문에

공정이 진화할수록 난이도가 어려지는 Rule입니다.

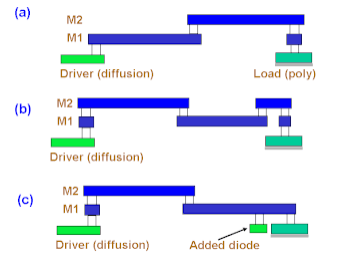

다음 그림은 antenna effect를 방지하기 위한 rule 내용입니다.

a) diffusion에 연결한다.

b) 너무 면적이 넓은 metal은 끊는다.

c) antenna diode를 삽입한다.

B를 좀더 정확히 하자면 하부메탈로 Jump 하는 것은 좋지 않습니다.

하부 floating metal의 plasma가 덜 제거 됐을 경우에 안 좋은 영향을 끼칠 수 있기 때문입니다.

요렇게 상부 메탈로 점프 뛰는 게 좋습니다.

3. Antenna diode

Antenna effect를 방지하기 위한 방법으로 Antenna diode를 삽입하는 case도 있었습니다.

바로 요렇게 diode를 다는 것입니다.

Layout을 보자면 P+well위에 N+ diffuision이 있는 그림입니다.

gate oxide의 Breakdown Voltage가 넘어가기 전에

Diode의 BV를 넘어서면서 plasma가 diode로 빠져나가기 때문에

Antenna effect를 방지할 수 있습니다.

하지만 diode의 면적이 작다면 충분히 plasma charge를 빼지 못할 수 도 있기에

Antenna Rule 수식에 분모에 들어가기도 합니다.

'반도체 > 반도체에 대해서' 카테고리의 다른 글

| MIMO에 대해서 (0) | 2024.05.11 |

|---|---|

| FPGA vs ASIC (0) | 2024.04.25 |

| 메모리의 종류 및 현황 (1) | 2023.06.08 |

| [제품] STT-MRAM / MRAM (0) | 2023.05.26 |

| [제품] PRAM (0) | 2023.05.23 |