반도체 제조 공정이 나노미터 단위로 미세화됨에 따라, 층과 층 사이의 평탄도를 확보하는 CMP(Chemical Mechanical Polishing) 공정의 중요성은 비약적으로 커졌습니다. 단순히 표면을 매끄럽게 만드는 것을 넘어, 노광 공정(Photo lithography)에서 초점 심도(Depth of Focus, DOF) 마진을 확보하기 위해 원자 수준의 평탄화가 요구되기 때문입니다. 하지만 CMP는 물리적 연마 패드와 화학적 슬러리를 사용하기 때문에, 레이아웃의 Pattern Density에 따라 연마 효율이 달라지는 고유의 한계를 가집니다.

1. 패턴 밀도 불균형이 초래하는 물리적 결함: Dishing과 Erosion

CMP 공정 중에 연마 패드는 일정한 압력으로 웨이퍼 표면을 누르며 회전합니다. 이때 패턴이 조밀한 영역은 Metal이나 절연막(Oxide) 구조물들이 패드의 하중을 견고하게 지지해 주지만, 패턴이 없거나 희소한 영역은 패드가 물리적으로 휘어져 아래로 파고드는 현상이 발생합니다.

- 디싱(Dishing): 넓은 금속 배선의 중앙부가 주변 절연막보다 더 많이 깎여 나가 웅덩이처럼 파이는 현상입니다. 이는 배선의 단면적을 줄여 저항을 증가시키고, 결과적으로 신호 지연(RC Delay)을 초래합니다.

- 에로전(Erosion): 미세한 패턴이 밀집된 영역에서 주변 절연막까지 함께 과하게 연마되어 전체적인 높이가 낮아지는 현상입니다.

2. 더미 패턴(Dummy Pattern)의 공학적 설계

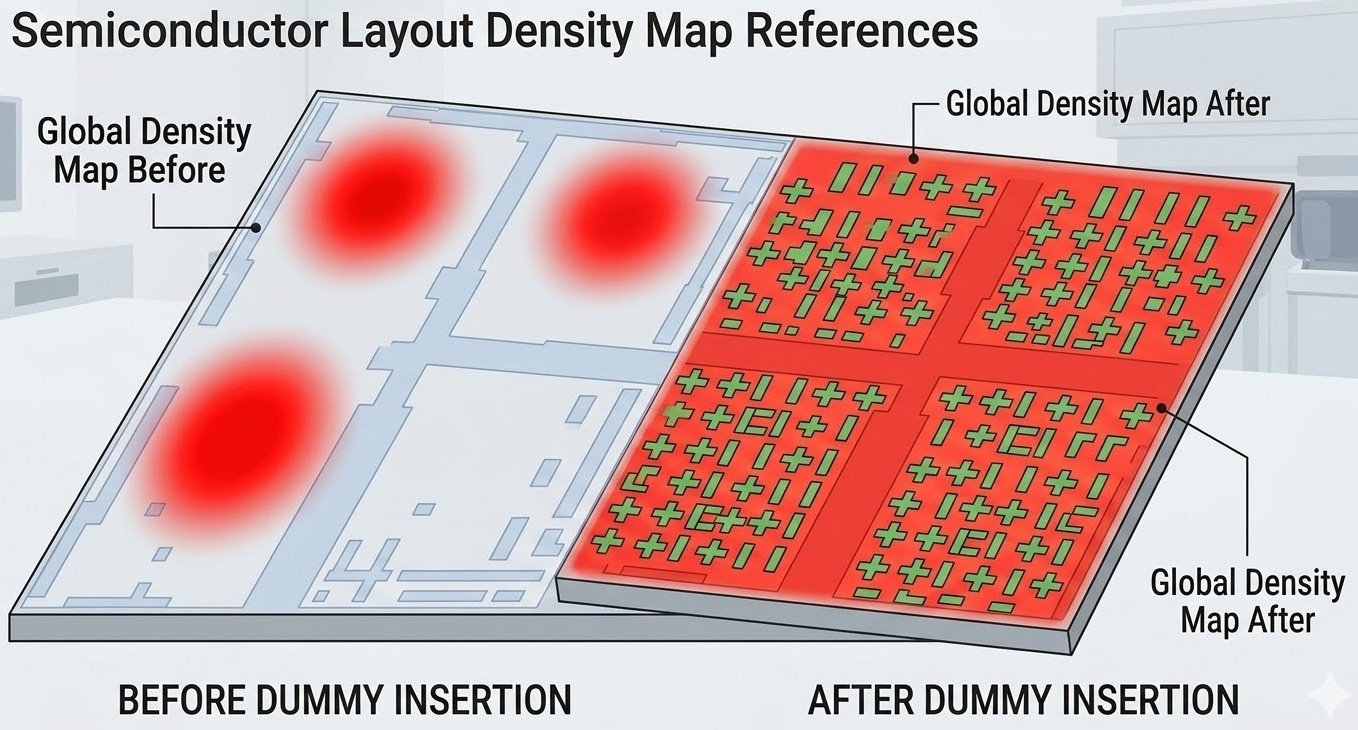

이러한 국부적인 연마 속도 차이를 극복하기 위해 도입된 것이 Dummy Pattern입니다. 설계자는 회로의 전기적 특성에는 영향을 주지 않으면서, 물리적으로는 연마 패드를 지지할 수 있는 Dummy Pattern을 배치합니다.

과거에는 단순히 격자 형태의 금속 조각을 채워 넣는 방식을 사용했지만, 최근의 고성능 칩 설계에서는 더미 패턴이 유발하는 Parasitic Capacitance까지 고려합니다. 의도치 않게 삽입된 Dummy Metal이 인접한 실제 Signalr과 커플링을 일으켜 신호 간섭을 유발할 수 있기 때문입니다. 이를 해결하기 위해 최근에는 다음과 같은 정교한 기법이 사용됩니다.

- Small Floating Dummies: 아주 작은 크기의 더미를 흩뿌려 기생 캡 영향을 최소화합니다.

- Grounded Dummies: 더미를 접지(GND)에 연결하여 전기적 노이즈 차폐 효과를 노리기도 합니다.

- Layer-specific Shapes: 각 층의 금속 특성에 따라 사각형, 십자형 등 최적화된 형태의 더미를 사용합니다.

3. DFM(제조 고려 설계)의 핵심 지표

결과적으로 더미 패턴 삽입은 DFM(Design for Manufacturability)의 핵심 공정입니다. 레이아웃 검증 단계에서 수행되는 Density Check는 단순히 룰을 통과하기 위한 절차가 아니라, 칩 전체의 높이 균일도(Planarity)를 제어하여 후속 공정인 Litho 시 빛의 초점이 칩 전체에 고르게 맺히도록 보장하는 작업입니다. 만약 특정 영역의 밀도가 낮아 평탄화에 실패하면, 그 위층에 그려지는 미세 회로는 초점이 흐려져 단선이나 합선 등의 치명적인 수율 저하로 이어지게 됩니다.

"현대 반도체 설계에서 더미 패턴은 단순한 '빈칸 채우기'가 아닙니다. 이는 공정의 변동성(Process Variation)을 설계 단계에서 선제적으로 제어하는 신뢰성 설계의 정수입니다. 엔지니어는 Density 룰을 맞추는 동시에, 이것이 유발할 수 있는 기생 성분이 회로 타이밍에 미치는 영향까지 계산에 넣어야 합니다."

'반도체 > 반도체 레이아웃' 카테고리의 다른 글

| 칩의 생존을 위협하는 두 적: GIDL과 DIBL 완벽 정리 (0) | 2026.03.15 |

|---|---|

| 반도체의 수직 혈관 TSV, 설계와 공정 관점 (0) | 2026.03.11 |

| 자주 나오지만 찾기 힘든 불량; Latch up 이란? (0) | 2026.03.07 |

| P&R (Place & Route), Physical Design Layout 엔지니어 (0) | 2026.02.26 |

| Layout Verification Layout (PDK/룰덱) 엔지니어의 세계 (0) | 2026.02.25 |