CMOS 구조 내부에서 의도치 않게 형성된 기생 소자(Parasitic BJT)들이 서로 연결되어, 과 접지(GND) 사이에 거대한 전류 통로가 생겨버리는 현상입니다. 한 번 켜지면 전원을 끄기 전까지 멈추지 않고 전류가 흐르기 때문에 '래치(Latch, 걸쇠)'라는 이름이 붙었습니다.

왜 발생하는가? (기생 소자의 형성)

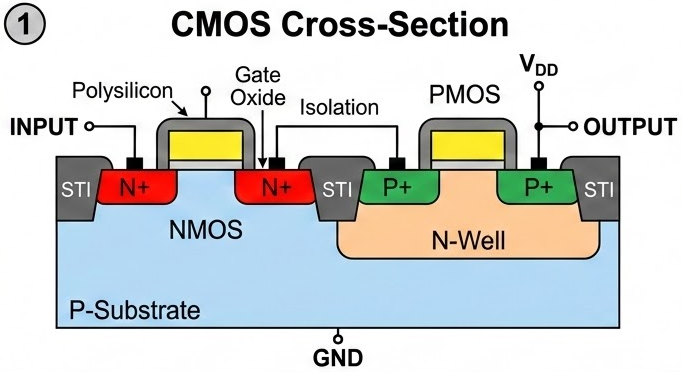

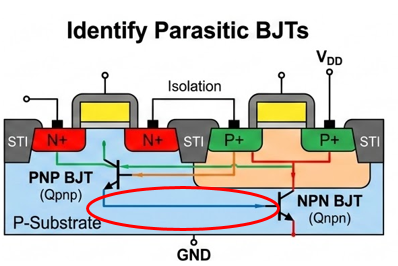

이미지 1, 2번에서 보시는 것처럼, CMOS는 NMOS와 PMOS를 만들기 위해 P형 기판과 N-well을 혼합해서 사용합니다. 이 과정에서 설계자가 의도하지 않은 PNP 트랜지스터와 NPN 트랜지스터가 만들어집니다.

PMOS 측에서 형성되는 이 소자는 다음과 같은 세 영역이 수직/수평으로 겹쳐지며 발생합니다.

- 에미터(Emitter): PMOS의 Source 영역입니다.

- 베이스(Base): PMOS가 놓여 있는 N-Well 영역 자체입니다.

- 컬렉터(Collector): N-Well을 감싸고 있는 P-Substrate입니다.

NMOS 측에서 형성되는 이 소자는 다음과 같은 영역들이 겹쳐지며 발생합니다.

- 에미터(Emitter): NMOS의 Source 영역입니다.

- 베이스(Base): NMOS가 놓여 있는 P-Substrate 영역입니다.

- 컬렉터(Collector): 인접한 PMOS의 N-Well 영역입니다.

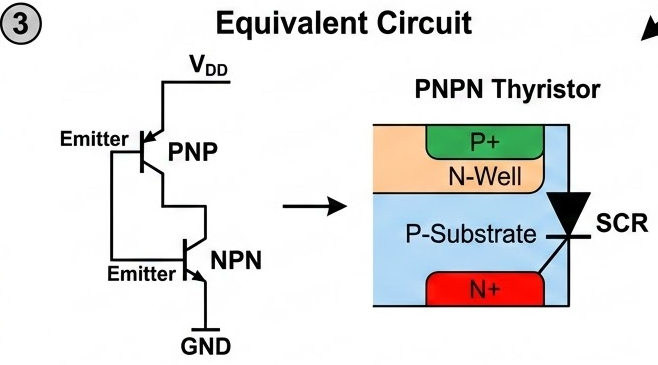

이것을 등가회로로 나타내면 아래 그림과 같습니다.

여기서 Latch-up이 주로 일어나는 부분은 P-Substrate입니다.

주로 guarding으로 GND를 제대로 못잡아서 그런데요, 그러면 저 위의 그림의 빨간색 동그라미 부분의 bias가 뜨게 되고 Latch-up이 시작됩니다

시작은 기판이나 Well에 전류가 흘러 전압 강하가 발생합니다. 이 전압 차가 BJT의 문턱 전압(약 0.7V)을 넘으면 하나의 BJT가 켜집니다. 켜진 BJT가 전류를 흘리면, 그 전류가 다시 상대방 BJT의 베이스를 자극하여 켭니다. 두 BJT가 서로를 계속 켜주는 Positive Feedback 상태에 빠지며, 전원과 접지가 직접 연결된 것처럼 엄청난 전류가 흐르게 됩니다.

해결 방법은 layout 상황에 따라 다르지만 guardring에 contact을 빵빵하게 박는 방법을 주로 사용합니다.

'반도체 > 반도체 레이아웃' 카테고리의 다른 글

| 반도체의 수직 혈관 TSV, 설계와 공정 관점 (0) | 2026.03.11 |

|---|---|

| CMP(Chemical Mechanical Polishing)와 Dummy Pattern (0) | 2026.03.10 |

| P&R (Place & Route), Physical Design Layout 엔지니어 (0) | 2026.02.26 |

| Layout Verification Layout (PDK/룰덱) 엔지니어의 세계 (0) | 2026.02.25 |

| 2D 도면이 3D FinFET이 되기까지: 단계별 공정 해설 (0) | 2026.02.09 |